杏彩登录注册网页版·涨知识:碳化硅产业链图谱

>杏彩登录注册网页版·

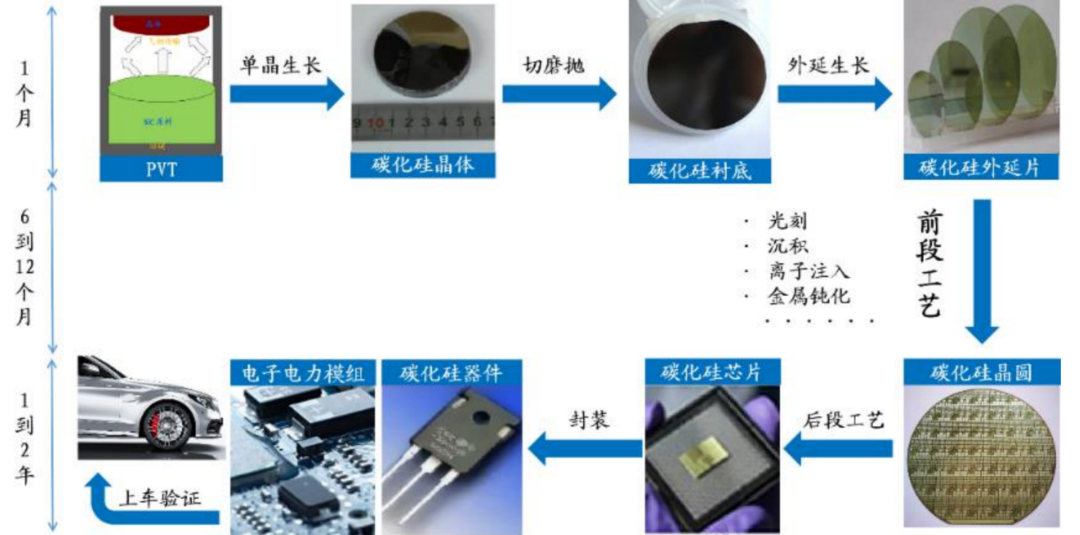

1)单晶生长,以高纯硅粉和高纯碳粉作为原材料形成碳化硅晶体;2)衬底环节,碳化硅晶体经过切割、研磨、抛光、清洗等工序加工形成单晶薄片,也即半导体衬底材料;

4)晶圆加工,通过光刻、沉积、离子注入和金属钝化等前段工艺加工形成的碳化硅晶圆,经后段工艺可制成碳化硅芯片;

碳化硅产品从生产到应用的全流程历时较长。以碳化硅功率器件为例,从单晶生长到形成衬底需耗时1 个月,从外延生长到晶圆前后段加工完成需耗时6-12 个月,从器件制造再到上车验证更需1-2 年时间。对于碳化硅功率器件IDM厂商而言,从工业设计、应用等环节转化为收入增长的周期非常之长,汽车行业一般需要4-5 年。

由SiC 粉经过长晶、加工、切割、研磨、抛光、清洗环节最终形成衬底。其中SiC晶体的生长为核心工艺,核心难点在提升良率。类型可分为导电型、和半绝缘型衬底,分别用于功率和射频器件领域。

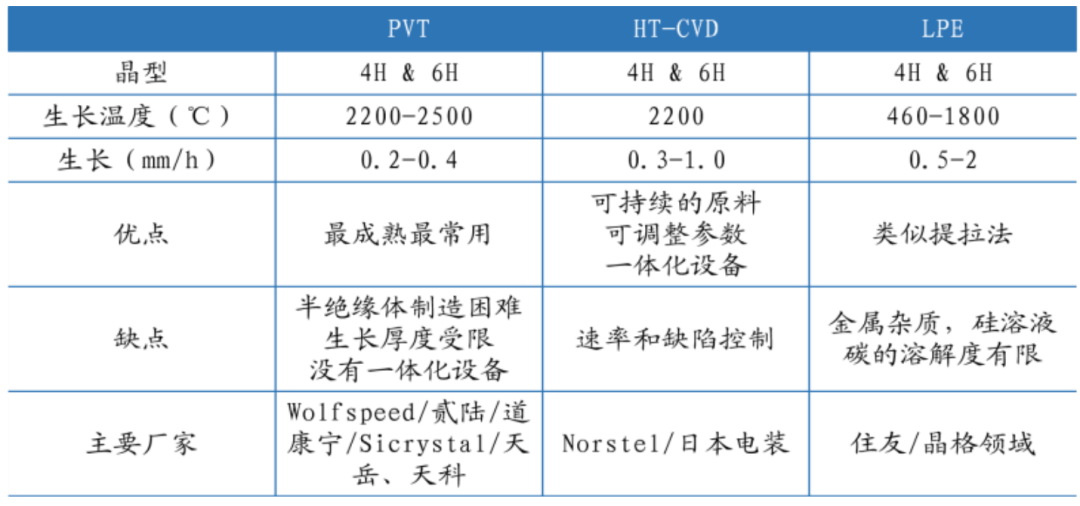

就技术路线而言,碳化硅的单晶生产方式主要有物理气相传输法(PVT)、高温气相化学沉积法(HT-CVD)、液相法(LPE)等方法,目前商用碳化硅单晶生长主流方法为相对成熟的PVT 法。

PVT:生长系统稳定性不佳、晶体生长效率低、易产生标晶型杂乱以及各种结晶缺陷等严重质量问题,从而成本较高。

HT-CVD:起步晚,能够制备高纯度、高质量的半绝缘碳化硅晶体,但设备昂贵、高纯气体价格不菲。

LPE:尚未成熟,可以大幅降低生产温度、提升生产速度,且在此方法下熔体本身更易扩型,晶体质量亦大为提高,因而被认为是碳化硅材料走向低成本的较好路径,有积极的发展空间。

目前6 英寸碳化硅衬底价格在1000美金/片左右,数倍于传统硅基半导体,核心降本方式包括:提升材料使用率(向大尺寸发展)、降低制造成本(提升良率)、提升生产效率(更成熟的长晶工艺)。

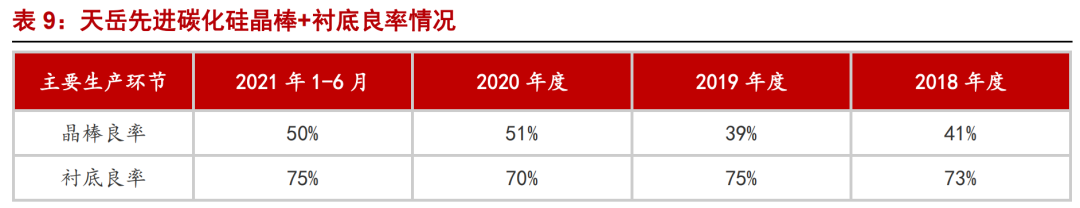

长晶端:SiC包含 200多种同质异构结构的晶型,但只有4H 型(4H-SiC)等少数几种是所需的晶型。而PVT 长晶的整个反应处于2300°C高温、完整密闭的腔室内(类似黑匣子),极易发生不同晶型的转化,任意生长条件的波动都会影响晶体的生长、参数很难精确调控,很难从中找到最佳生长条件。目前行业主流良率在50-60%左右(传统硅基在90%以上),有较大提升空间。

机加工端:碳化硅硬度与金刚石接近(莫氏硬度达9.5),切割、研磨、抛光技术难度大,工艺水平的提高需要长期的研发积累。目前该环节行业主流良率在70-80%左右,仍有提升空间。

提升生产效率(更成熟的长晶工艺):SiC长晶的速度极为缓慢,行业平均水平每小时仅能生长0.2-0.3mm,较传统晶硅生长速度相比慢近百倍以上。未来需PVT 工艺的进一步成熟、或向其他先进工艺(如液相法)的延伸。

SiC衬底设备主要包括:长晶炉、切片机、研磨机、抛光机、清洗设备等。与传统传统晶硅设备具相通性、但工艺难度更高,设备+工艺合作研发是关键。

本质是在衬底上面再覆盖一层薄膜以满足器件生产的条件。具体分为:导电型SiC 衬底用于SiC 外延,进而生产功率器件用于电动汽车以及新能源等领域。半绝缘型SiC 衬底用于氮化镓外延,进而生产射频器件用于5G通信等领域。

全球SiC外延设备被行业四大龙头企业Axitron、LPE、TEL和Nuflare垄断,并各具优势。

SiC功率器件的生产分为芯片设计、制造和封装测试环节,产品包括SiC 二级管、SiCMOSFET、全SiC 模块(SiC二级管和 SiCMOSFET 构成)、SiC混合模块(SiC二级管和 SiCIGBT 构成)。目前中国碳化硅期间厂商以IDM为主,少量为纯设计企业。

文章出处:【微信号:today_semicon,微信公众号:今日半导体】欢迎添加关注!文章转载请注明出处。

特色工艺模块简介 /

的5大优势 /

迭代趋势与背后的意义、合作与机会 /

化发展趋势 /

行业加速发展 /

衬底类型及应用 /

主要包括衬底、外延、器件设计、制造、封测等环节。上游是衬底和外延、中游是器件和模块制造,下游是终端应用。

-

05-08

杏彩登录注册网页 昆仑山下的钢轨“抛光师”

进入4月,昆仑山上仍被白雪覆盖。1日一早,在昆仑山脚下的格库铁路格尔木至格尔木南上行联

-

05-08

杏彩登录注册网页 “税动力”赋能粤企研发创新培育发展新质生产力

南都讯 记者卢婉珊 通讯员岳瑞轩 近期,国家税务总局广东省税务局举办以“春风暖企 向新

-

05-08

杏彩登录注册网页 税惠赋能 广东产业凝聚向“新”力

近日,国家税务总局广东省税务局以“春风暖企 向新而进”为主题展开调研,先后走进广州、佛

-

05-08

杏彩登录注册网页 磁力抛光机和磁力研磨机的功能和适用范围对比分析

虽然它们在功能和原理上有一些相似之处,但仍然有一些区别,因为两者在结构、使用方式和适用

咨询热线:13827035023 (李先生)

咨询热线:13827035023 (李先生)